| Herwig Siebenhofer / Home / C64 |

|

• Memory Map

• Float Map

• ROM Map

• Basic ROM

• Kernal ROM

• Char ROM

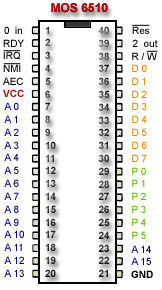

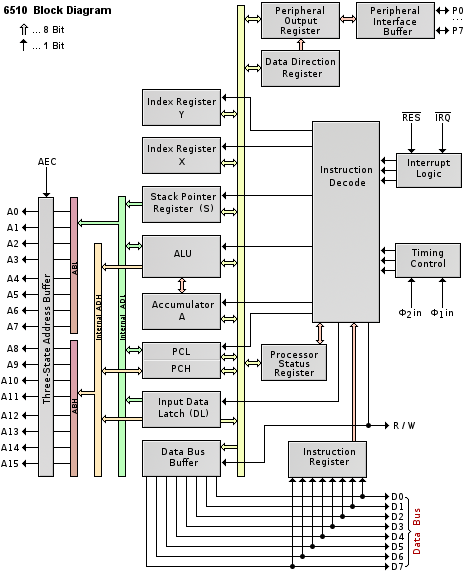

• CPU 6510

• VIC 6569

• SID 6581

• CIA 6526

• PLA

• Keyboard

• Control-Ports

• sonstige Ports

• Bauteile

• Schematik 1

• Schematik 2

• HF-Modulator

• Datasette

• Reset

C 1541 Floppy

• Blockschaltbild

• Memory Map

• Rom Listing

• Schematik

• VIA 6522

• Service

C 1581 Floppy

• Memory Map

• Rom Listing

• Schematik

• CIA 8520

• WD 1772

Archiv

• Mouse 1531

• Float-Formate

• Screenshots

• Korrekturen

• Chip 74xx

|

CPU 6510 Der MOS 6510 überblendet die Speicherstellen 0000h und 0001h mit den CPU-internen Steuerregistern. Diese können durch normale Speicherzugriffe gelesen und geschrieben werden.

|